### **Performance Characteristics**

RF/LO frequency range: 20GHz~55GHz

IF frequency range: DC~16GHz Conversion loss: 9dB (typical value) LO-RF isolation: 30dB (typical value)

RF input P1dB: -3dB

Local oscillator driving power: 8dBm

DC power supply: Vg=-0.5V

Chip size: 1.60 mm x 2.00 mm x 0.07 mm

### **Product Introduction**

The Q-band broadband mixer chip covers a frequency range of 20GHz~55GHz, with a typical frequency conversion loss of 9dB, a typical local oscillator RF isolation of 30dB, and an RF input P1dB of -3dBm. Can achieve up and down mixing.

## Electrical Performance (TA= +25 °C, L0= 8dBm, Vg= -0.5V)

| Index                             | Min | Тур | Max | Unit |

|-----------------------------------|-----|-----|-----|------|

| RF frequency range                | 20  |     | 55  | GHz  |

| Local oscillator frequency range  | 20  |     | 55  | GHz  |

| Intermediate frequency range      | DC  |     | 16  | GHz  |

| SSB frequency conversaion loss    | 8   |     | 10  | dB   |

| Local oscillator/<br>RF isolation | 20  | 30  | 50  | dB   |

| RF IN P1dB                        |     | -3  |     | dBm  |

| Local oscillator power            | 6   | 8   | 13  | dBm  |

| RF port standing wave             | 12  | 2   | 35  | 34   |

| Standing wave at IF port          | 13  | 15  | 2   | 343  |

### **Use Restriction Parameters**

| RF Input Power               | 10dBm       |  |

|------------------------------|-------------|--|

| Local Oscillator Input Power | 15dBm       |  |

| Negative Gate Voltage        | -1V         |  |

| Storage Temperature          | -65°C~150°C |  |

| Operating Temperature        | -55°C~85°C  |  |

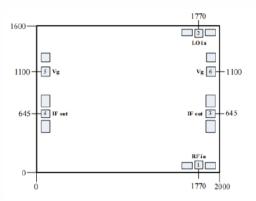

### **External Dimensions**

Note:

- I) All dimensions marked are in micrometers (μm);

- 2) Dimensional tolerance for external dimensions: ±50µm;

- $\overset{,}{3}$ ) The chip thickness is 70 $\mu m$ .

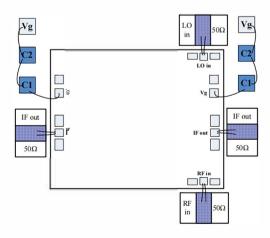

### **Bonding Pressure Point Definition**

| No. | Symbol | Function                                                                                                                            | Size(µm <sup>2</sup> ) |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 1   | RF in  | RF signal input terminal,<br>external 50 ohm system, no<br>need for DC isolation capacitor.                                         | 86X72                  |

| 2   | LO in  | The local oscillator signal input terminal is connected to an external 50 ohm system and does not require a DC isolation capacitor. | 86X86                  |

| 3.4 | IF out | Intermediate frequency signal output terminal, externally connected to a 50 ohm system, with no DC blocking capacitor on the chip.  | 100X100                |

| 5.6 | Vg     | The gate voltage feeding terminal requires external 100F and 10000pF bypass capacitors.                                             | 100X100                |

### **Suggested Assembly Diagram**

Add: 101 cecil street #14-10, tong eng building singapore 069533

Email: info@standardcircuit.com

Web: www.standardcircuit.com Tel: +65 89472019

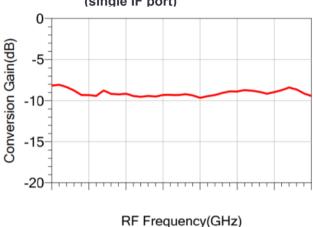

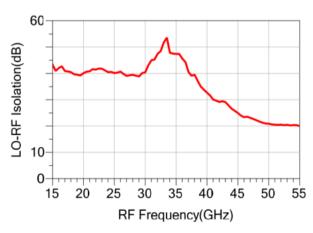

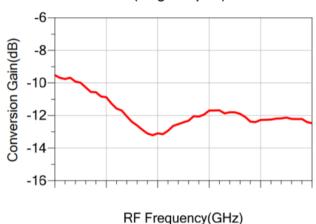

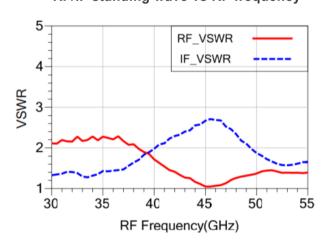

## On Chip Testing Curve CTA = +2s·c )

Freq\_IF= 1GHz, Freq\_IF= Freq\_RF-Freq\_LO; Pwr\_RF=-15dBm, Pwr\_L0=8dBm, Vg=-0.5V

## SSB frequency conversion loss VS RF frequency (single IF port)

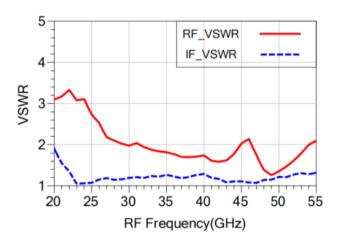

## RF/IF standing wave vs RF frequency

## Local oscillator RF isolation vs RF frequency

## On Chip Testing Curve $<T_A$ +2s c)

Freq\_L0=29.6GHz, Freq\_IF=Freq\_RF-Freq\_LO; Pwr\_RF=-15dBm, Pwr\_L0=8dBm, Vg=-0.5V

# SSB frequency conversion loss VS RF frequency (single IF port)

### RF/IF standing wave vs RF frequency

#### Note:

- 1) Storage: The chip must be placed in a container with electrostatic protection and stored in a nitrogen environment.

- 2) Cleaning treatment: Bare chips must be operated and used in a purified environment, and it is prohibited to use liquid cleaning agents to clean the chips.

- 3) Electrostatic protection: Please strictly comply with ESD protection requirements to avoid electrostatic damage.

- 4) Conventional operation: To retrieve the chip, please use a vacuum chuck or precision pointed tweezers. During the operation, avoid touching the chip surface with tools or fingers.

- 5) Power on sequence: When powering on, apply gate voltage first, then drain voltage; When powering off, first remove the leakage voltage, then remove the gate voltage.

- 6) Mounting operation: Chip installation can use AuSn solder eutectic sintering or conductive adhesive bonding process. The mounting surface must be clean and flat, and the gap between the chip and the input/output RF connection substrate should be minimized as much as possible.

**Sintering process:** Use 80/20 AuSn for sintering, the sintering temperature should not exceed 300 °C, the sintering time should be as short as possible, not exceeding 20 seconds, and the friction time should not exceed 3 seconds

**Adhesive process:** When bonding conductive adhesive, try to minimize the amount of glue applied, and refer to the information provided by the conductive adhesive manufacturer for curing conditions.

7) Keying operation:

Unless otherwise specified, use 2 bonding wires (with a diameter of 25um) for RF input and output, and keep the bonding wires as short as possible.

Hot ultrasonic bonding temperature is 150 °C, using the smallest possible ultrasonic energy.

8) Please contact the supplier if you have any questions.