## Performance characteristics

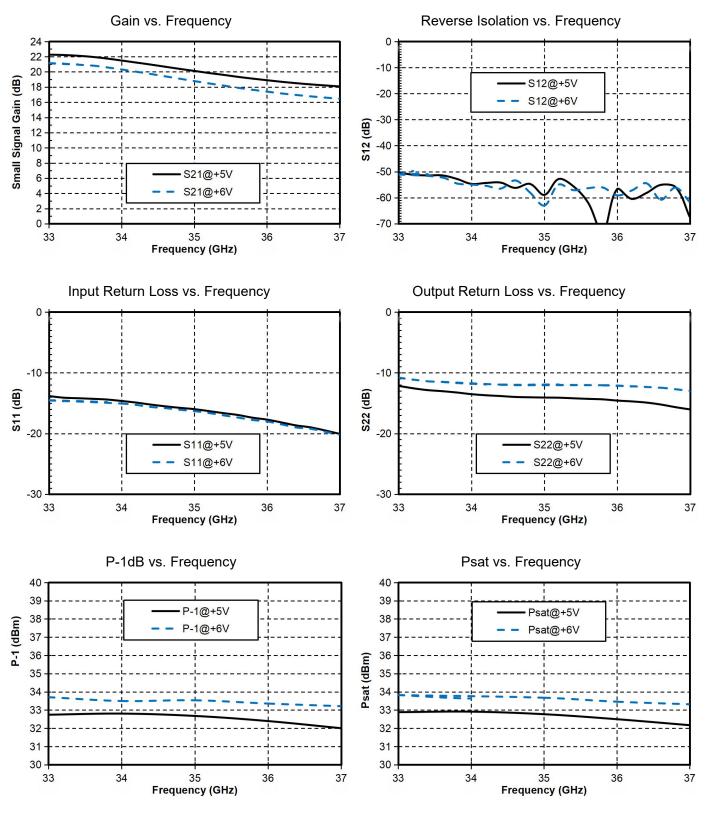

Frequency range: 33-37GHz Small Signal Gain: 20 dB Gain flatness : ± 2.2 dB P-1dB: 33 dBm Psat: 33 dBm Power supply: + 6V@1300mA 500hm input/output 100% on-chip testing Chip size : 2.35 x 2.91 x 0.1mm

### **Product Introduction**

GPA -3337B is a broadband power amplifier chip based on GaAs process , covering the frequency range of 33 ~37GHz, with a small signal gain of 20dB and a Psat output power of 33dBm. The amplifier operates with +6V. The chip via metallization process ensures good grounding, and the back side is metallized for eutectic sintering process.

| Use restriction parameter <sup>1</sup> |              |  |  |

|----------------------------------------|--------------|--|--|

| Maximum drain voltage                  | +9 V         |  |  |

| Maximum gate bias                      | - 3 V        |  |  |

| Maximum input power                    | +25 dBm      |  |  |

| Operating temperature                  | -55 ~ +85°C  |  |  |

| Storage temperature                    | -65 ~ +150°C |  |  |

[1] Exceeding any of these maximum limits may cause permanent damage.

| Electrical parameters (Ta=+25°C, Vd = +6 V, Vg=-0.7V, Ids= 1300 mA)                |         |               |         |      |

|------------------------------------------------------------------------------------|---------|---------------|---------|------|

| index                                                                              | Minimum | Typical Value | Maximum | unit |

| Frequency Range                                                                    | 33-37   |               | GHz     |      |

| Small Signal Gain                                                                  | -       | 20            | -       | dB   |

| Gain Flatness                                                                      | ± 2.2   |               | dB      |      |

| P-1dB                                                                              | -       | 33            | -       | dBm  |

| Psat                                                                               | -       | 33            | -       | dBm  |

| Input return loss                                                                  | -       | 16            | -       | dB   |

| Output return loss                                                                 | -       | 11.5          | -       | dB   |

| * By tuning the Vg terminal voltage -2V~0V, the recommended gate voltage is -0.7V. |         |               |         |      |

## Main index test curve

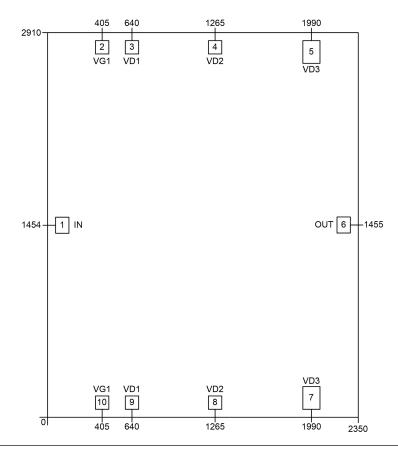

#### Appearance and structure (unit in the figure is micrometer)

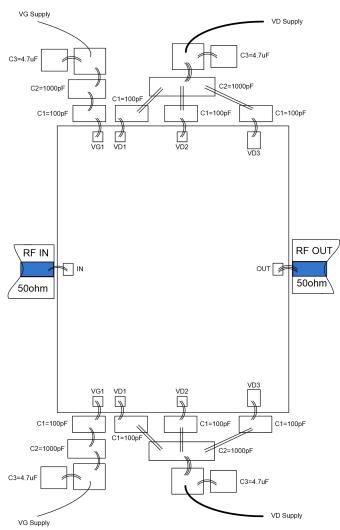

#### Bonding point definition Function Bonding point number **Functional Description** Symbol The signal input terminal is connected to a 50 ohm circuit, and no 1 **RF IN** DC blocking capacitor is required. The signal output terminal is connected to a 50 ohm circuit, and 6 **RF OUT** no DC blocking capacitor is required. Amplifier drain bias, external 100pF, 1000pF, 4.7uF bypass 3, 4, 5, 7, 8, 9 V D1~3 capacitors are required. Amplifier gate bias, external 100pF, 1000pF, 4.7uF bypass 2.10 VG1 capacitors are required. Chip bottom GND needs to be in good contact with the RF and DC grounds

Note: For high-power devices, three gold wires need to be soldered to the RF output terminal.

### Notice

- 1. The single-chip circuit needs to be stored in a dry and clean N2 environment;

- 2. The chip substrate material 6H-SiC is very brittle and must be used with care to avoid damaging the chip;

- 3. There is no insulating protective layer on the chip surface, so attention should be paid to the cleanliness of the assembly environment to avoid excessive contamination of the surface ;

- The thermal expansion coefficient of the carrier should be close to that of 6H-SiC , with a linear thermal expansion coefficient of 4.2×10-6/ °C . It is recommended that CuMoCu be used as the carrier material. CuMo or CuW ;

- 5. Avoid holes between the chip and the carrier during assembly, and ensure good heat dissipation between the box and the carrier;

- 6. It is recommended to use gold-tin solder for sintering, Au: Sn = 80%: 20%, the sintering temperature should not exceed 300 °C, the time should not be longer than 30 seconds, and the sintering process

should avoid rapid temperature changes and need to gradually increase and decrease the temperature;

- 7. It is recommended to use gold wire with a diameter of 25µm to 30µm, the temperature of the bonding platform chassis should not exceed 250 °C, the bonding time should be as short as possible, and the bonding process should avoid rapid temperature changes;

- 8. When power is on, the gate voltage is increased first and then the drain voltage is increased. When power is off, the drain voltage is reduced first and then the gate voltage is reduced.

- 9. has DC blocking capacitors for input and output , but the input end has a DC short-circuit structure to ground;

- 10. Pay attention to anti-static during chip use and assembly, wear a grounded anti-static bracelet, and ensure that the sintering and bonding tables are well grounded .