### Performance characteristics

- Frequency range:6-18GHz

- Small signal gain:21dB

- Noise figure: 1.5dB typ., 1.7dB max.

- P-1dB: 17dBm

- Power supply: +5V/85mA

- Input/Output: 500hm

- 100% on-chip testing

- Chip size: 1.6 x 0.8 x 0.09 mm

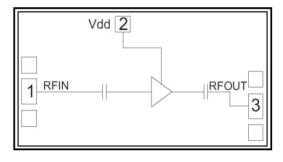

### Functional Block Diagram

### Product Introduction

GLA-0618E is a broadband low-noise amplifier chip, with a frequency range of 6GHz~18GHz, a small signal gain of 21dB, and an in band noise figure of 1.5dB. GLA-0618E is powered by a+5V single power supply.

| Electrical performance parameters |              |  |

|-----------------------------------|--------------|--|

| Maximum leakage voltage           | +7V          |  |

| Maximum input power               | +20dBm       |  |

| Working temperature               | -55 ~ +125°C |  |

| Storage temperature               | -65 ~ +150°C |  |

[1] Exceeding any of the above maximum limits may result in permanent damage.

| Electrical performance parameters( $T_A$ = +25°C, Vd=+5V) |               |               |               |      |  |  |

|-----------------------------------------------------------|---------------|---------------|---------------|------|--|--|

| Index                                                     | Minimum value | Typical value | Maximum value | Unit |  |  |

| Frequency range                                           |               | GHz           |               |      |  |  |

| Small signal gain                                         | 20.           | 21            | 21.5          | dB   |  |  |

| Gain flatness                                             |               | ±0.5          |               | dB   |  |  |

| Noise figure                                              | -             | 1.5           | 1.7           | Db   |  |  |

| P-1dB                                                     | 16.5          | 17            | 17.5          | dBm  |  |  |

| Psat                                                      | 17.5          | 18            | 18.5          | dBm  |  |  |

| Input return loss                                         | 13            | 16            | -             | dB   |  |  |

| Output return Loss                                        | 12            | 15            | -             | dB   |  |  |

| Static current                                            |               | 85            |               | mA   |  |  |

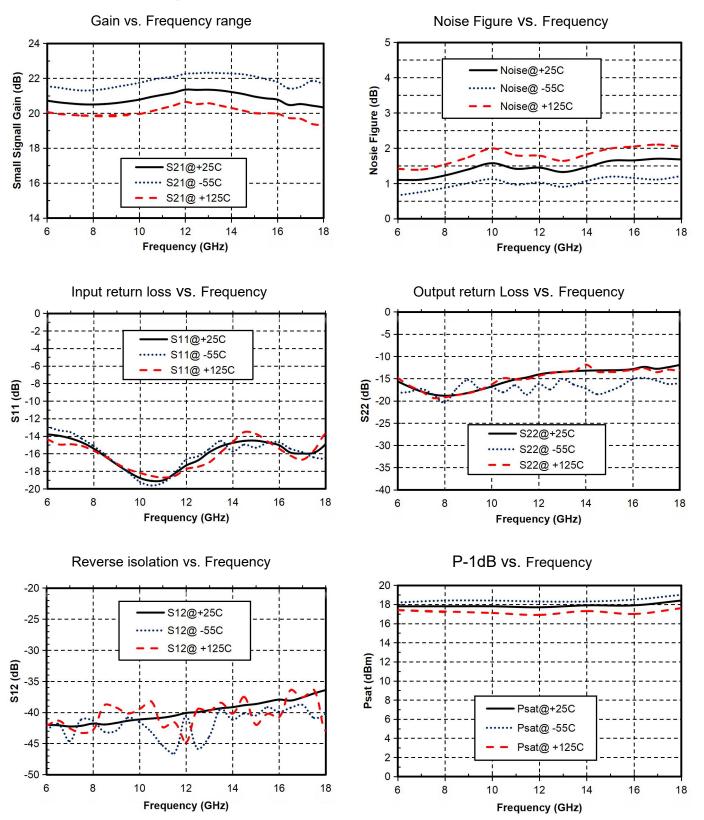

### Main indicator testing curve

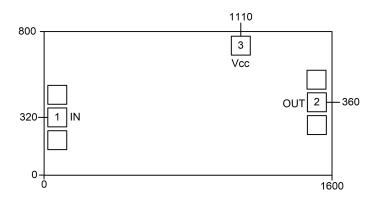

### External structure<sup>2</sup>

[2] The units in the figure are all millimeters

| Definition of bonding pressure point |                       |                                                                    |                    |  |  |

|--------------------------------------|-----------------------|--------------------------------------------------------------------|--------------------|--|--|

| Bond point number                    | Functional<br>symbols | Function Description                                               | Equivalent circuit |  |  |

| 1                                    | RFIN                  | RF signal input terminal, no need for                              |                    |  |  |

|                                      |                       | DC capacitors.                                                     |                    |  |  |

| 2                                    | RFOUT                 | RF signal output terminal, no need for                             |                    |  |  |

|                                      |                       | DC isolation capacitor.                                            |                    |  |  |

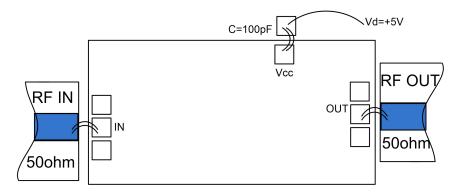

| 3                                    | VCC                   | Amplifier drain bias, requires an external 100pF bypass capacitor. | O Vdd              |  |  |

| Chip bottom                          | GND                   | The bottom of the chip needs to be well grounded with RF and DC.   |                    |  |  |

### Recommended assembly diagram

#### Notice

- The chip needs to be stored in a container with anti-static function and stored in a nitrogen environment.

- Attempting to clean the surface of bare chips using wet chemical methods is prohibited.

- Please strictly comply with ESD protection requirements to avoid static damage to bare chips.

- Routine operation: Please use precision pointed tweezers to remove the bare chip. During the operation, avoid tools or fingers touching the surface of the chip.

- Suggestion for mounting operation: Bare chip installation can use AuSn solder eutectic sintering or conductive adhesive bonding process. The installation surface must be clean and flat.

- Sintering process: It is recommended to use AuSn solder sheets with a gold tin ratio of 80/20. The working surface temperature reached 255 °C, and the tool (vacuum chuck) temperature reached 265 °C. When a high-temperature mixed gas (nitrogen to hydrogen ratio of 90/10) is blown onto the chip, the temperature at the top of the tool should be raised to 290 °C. Do not let the chip stay above 320 °C for more than 20 seconds. The friction time should not exceed 3 seconds.

- Bonding process: The amount of conductive adhesive applied should be as small as possible. After placing the chip in the installation position, the conductive adhesive can be vaguely visible around it. Please follow the information provided by the conductive adhesive manufacturer for curing conditions.

- Suggestion for bonding operation: Both spherical or wedge-shaped bonding should be used Φ 0.025mm (1mil) gold wire. Thermal ultrasonic bonding temperature is 150 °C. The pressure of the spherical bonding cutter is 40-50GF, and the pressure of the wedge bonding cutter is 18-22GF. Use as little ultrasonic energy as possible. The bonding process starts at the pressing point on the chip and ends at the packaging (or substrate).